【FreeRTOS】第一章:介绍

创始人

2024-05-22 03:09:31

0次

- FreeRTOS是什么?

Free和RTOS,Free就是免费的、自由的意思,RTOS 全称是 Real Time Operating System。中文名就是实时操作系统。可以看出FreeROTS 就是一个免费的 RTOS 类系统。这里要注意,RTOS 不是指某一个确定的系统,而是指一类系統。比如 UCOS,FreeRTOS,RTX,RT-Thread 等都是RTOS 类操作系統。操作系统允许多个任务同时运行,这个叫做多任务,实际上,一个处理器核心在某一时刻只能运行一个任务。操作系统中任务调度器的责任就是決定在某一时刻究竟运行哪个任务,任务调度在各个任务之间的切换非常快!这就给人们造成了同一时刻有多个任务同时运行的错觉。操作系统的分类方式可以由任务调度器的工作方式决定,比如有的操作系统给每个任务分配同样的运行时间,时间到了就轮到下一个任务,Unix 操作系统就是这样的。RTOS 的任务调度器被设计为可预测的,而这正是嵌入式实时操作系统所需要的,实时环境中要求操作系统必须对某一个事件做出实时的响应,因此系统任务调度器的行为必须是可预测的。像 FreeRTOs 这种传统的RTOS类操例系统是由用户给每个任务分配一个任务优先级,任务调度器就可以根据此优先级来决定下一刻应该运行哪个任务。

FrceRTOS 是 RTOS 系统的一种,FreCRTOS 十分的小巧,可以在资源有限的徽控制器中运行,当然了,FreeRTOS 不仅局限于在微控制器中使用 - 为什么选择FreeRTOS?

1.免费

2.简单,文件少

3.ST有cubemx工具能直接生成工程方便移植

4.文档齐全

5.社会占有量高 - FreeRTOS优点

FreeRTOS 是一个可裁剪的小型 RTOS 系统,其特点包括:

FreeRTOS 的内核支持抢占式,合作式和时间片调度。

提供了一个用于低功耗的 Tickless 模式。

系统的组件在创建时可以选择动态或者静态的 RAM,比如任务、消息队列、信号量、软件定时器等等。

FreeRTOS-MPU 支持 Corex-M 系列中的 MPU 单元,如 STM32F429。

FreeRTOS 系统简单、小巧、易用,通常情况下内核占用 4k-9k 字节的空间。

高可移植性,代码主要 C 语言编写。

高效的软件定时器。

强大的跟踪执行功能。

堆栈溢出检测功能。

任务数量不限。

任务优先级不限。 - FreeRTOS源码

https://www.freertos.org/zh-cn-cmn-s/

5.STMcubemx简单使用FreeRTOSV1

5.STMcubemx简单使用FreeRTOSV1

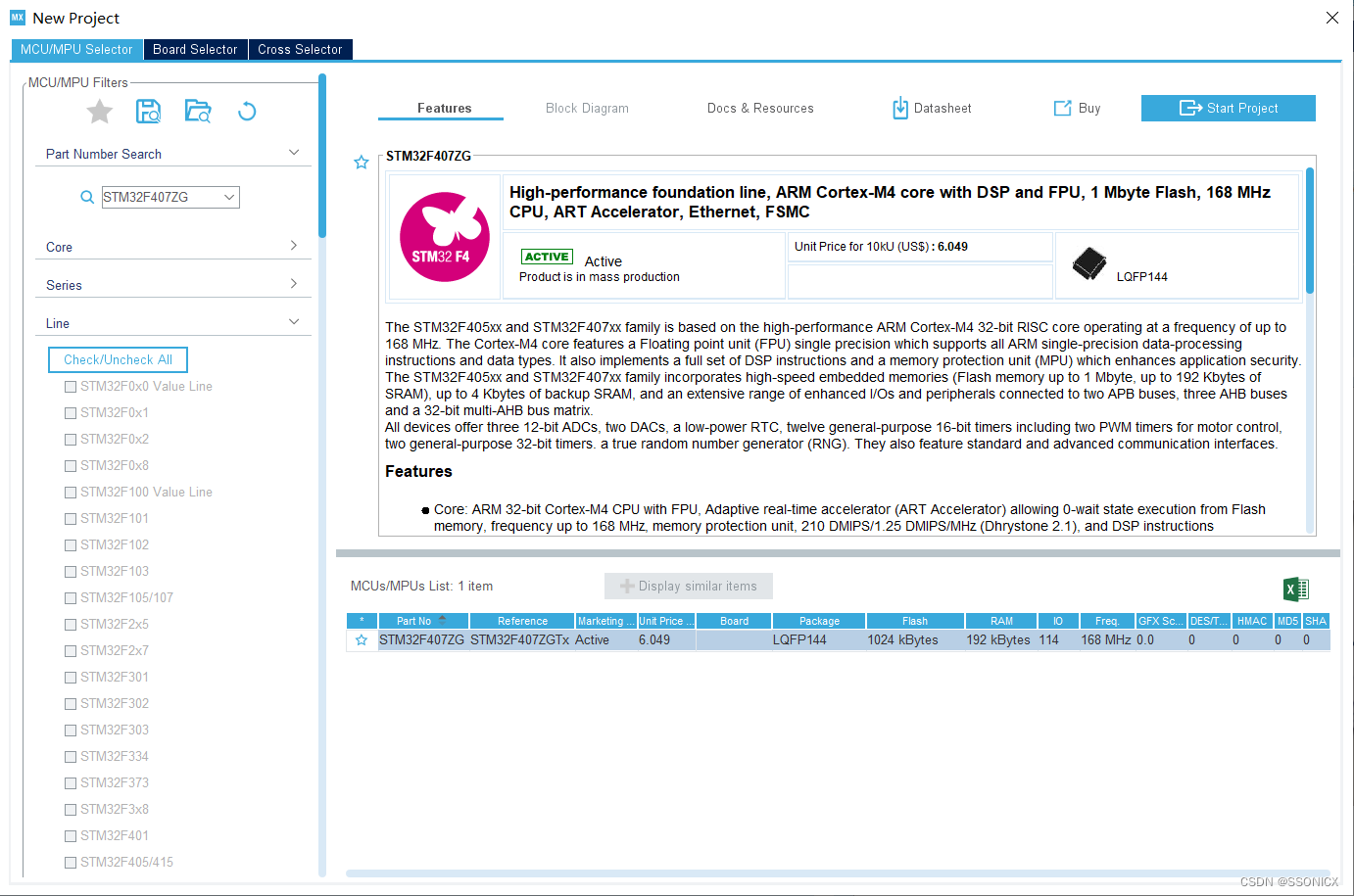

以上是测试例程使用的主控芯片型号:STM32F407ZGT6

以上是测试例程使用的主控芯片型号:STM32F407ZGT6

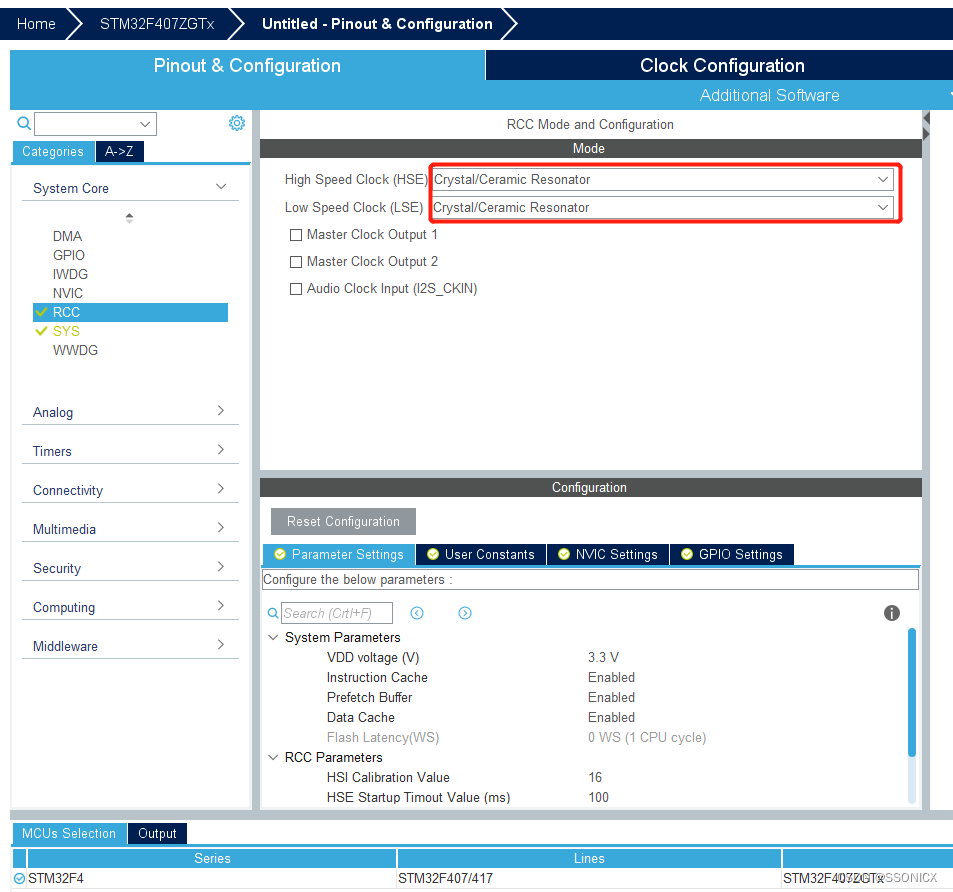

选择外部晶振,比内部晶振稳定频率更高

选择外部晶振,比内部晶振稳定频率更高

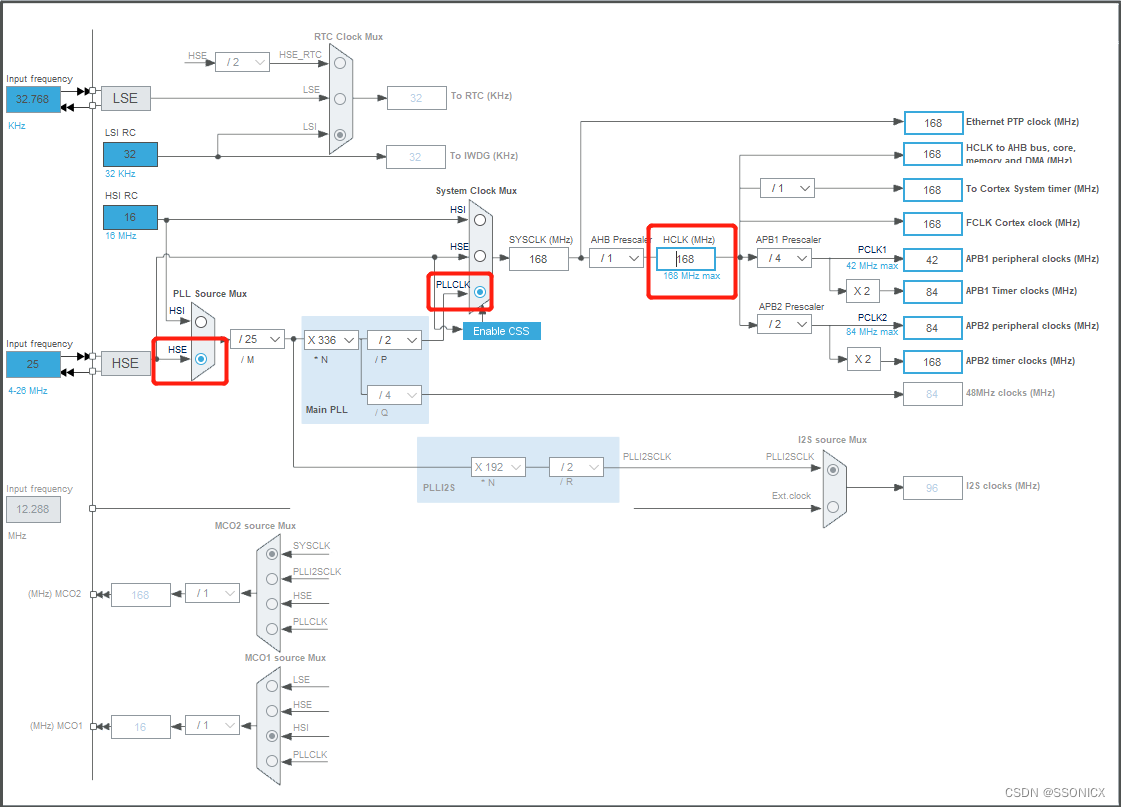

把高速外部时钟,25M晶振接入倍频器,使HCLK达到168MHZ的最高频率

把高速外部时钟,25M晶振接入倍频器,使HCLK达到168MHZ的最高频率

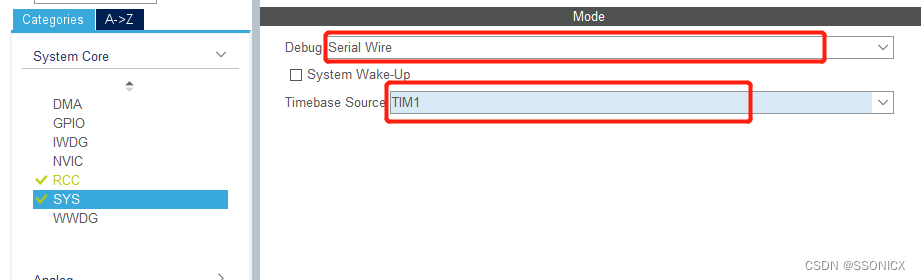

Debug 修改为Serial wire,通过SWD方式下载代码

Debug 修改为Serial wire,通过SWD方式下载代码

Timebase Source:时间基源 改为定时器1,systick留给FreeRTOS内核使用

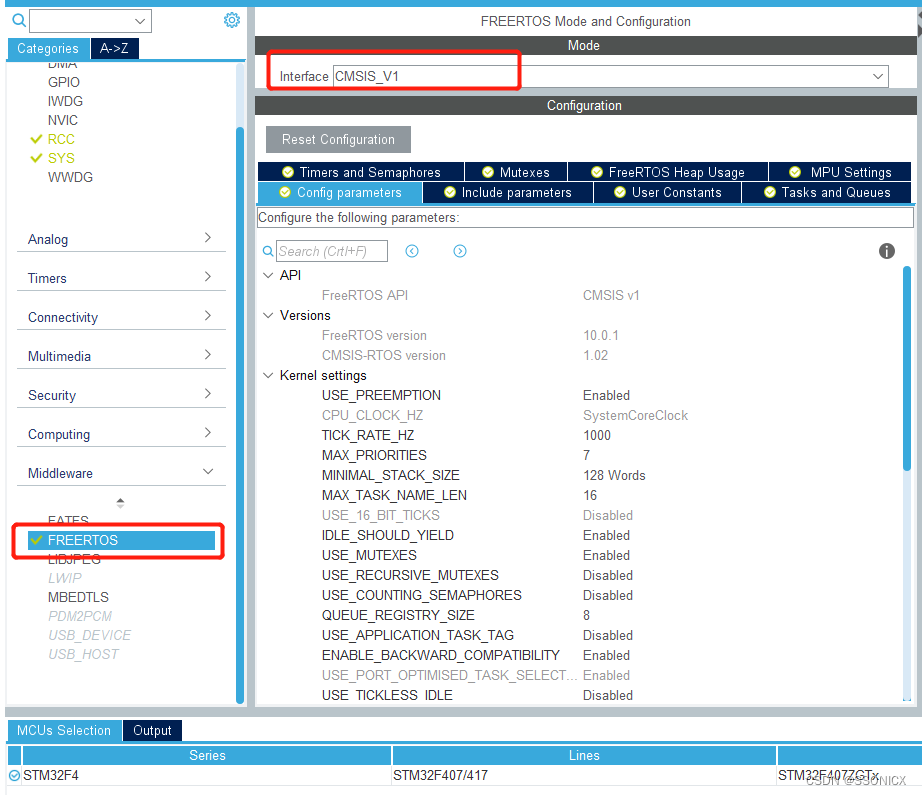

项目使用FreeRTOS的V1版本

项目使用FreeRTOS的V1版本

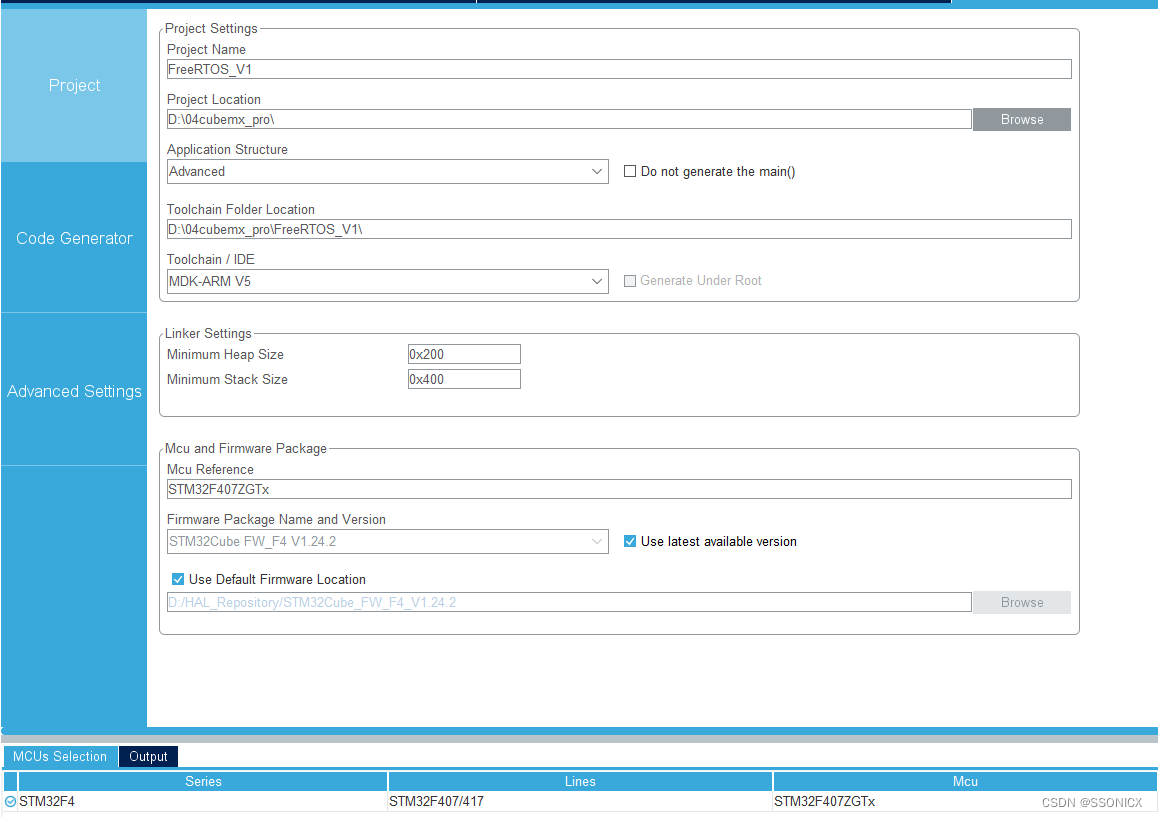

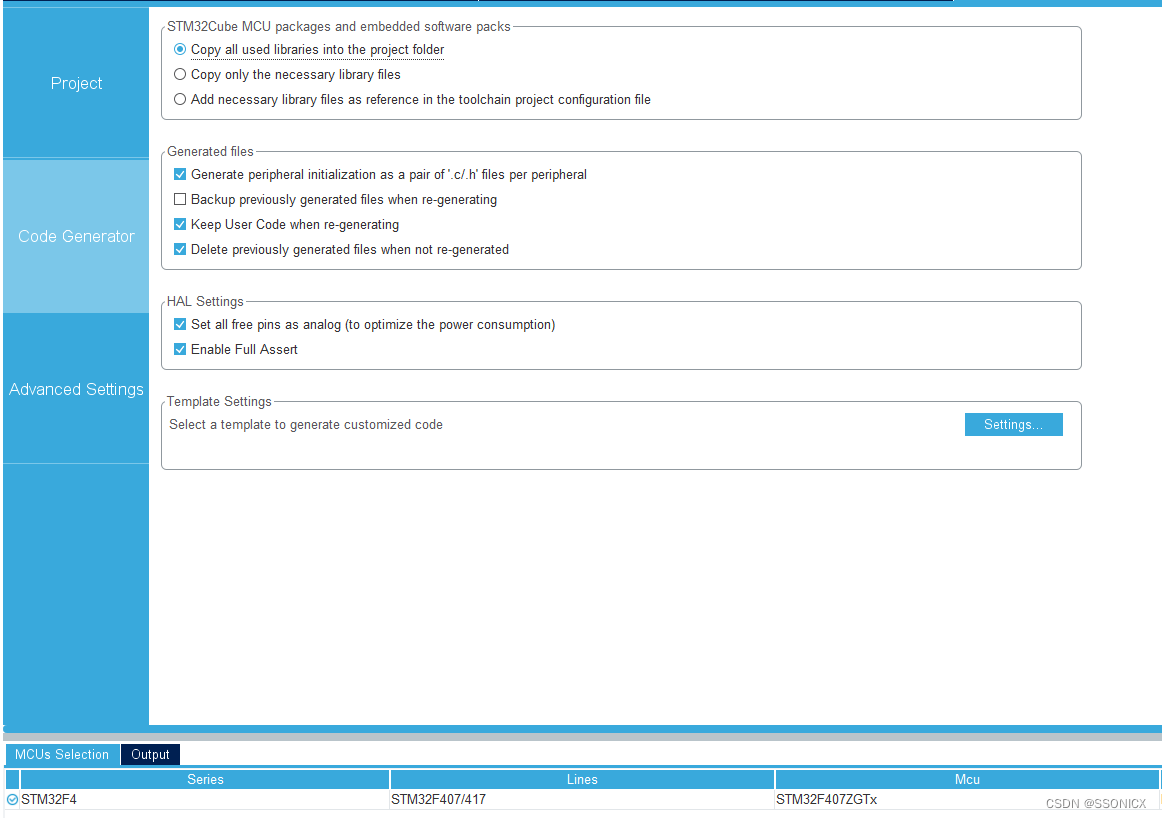

按上述设置完后,点击生成工程

按上述设置完后,点击生成工程

上图代表工程生成成功

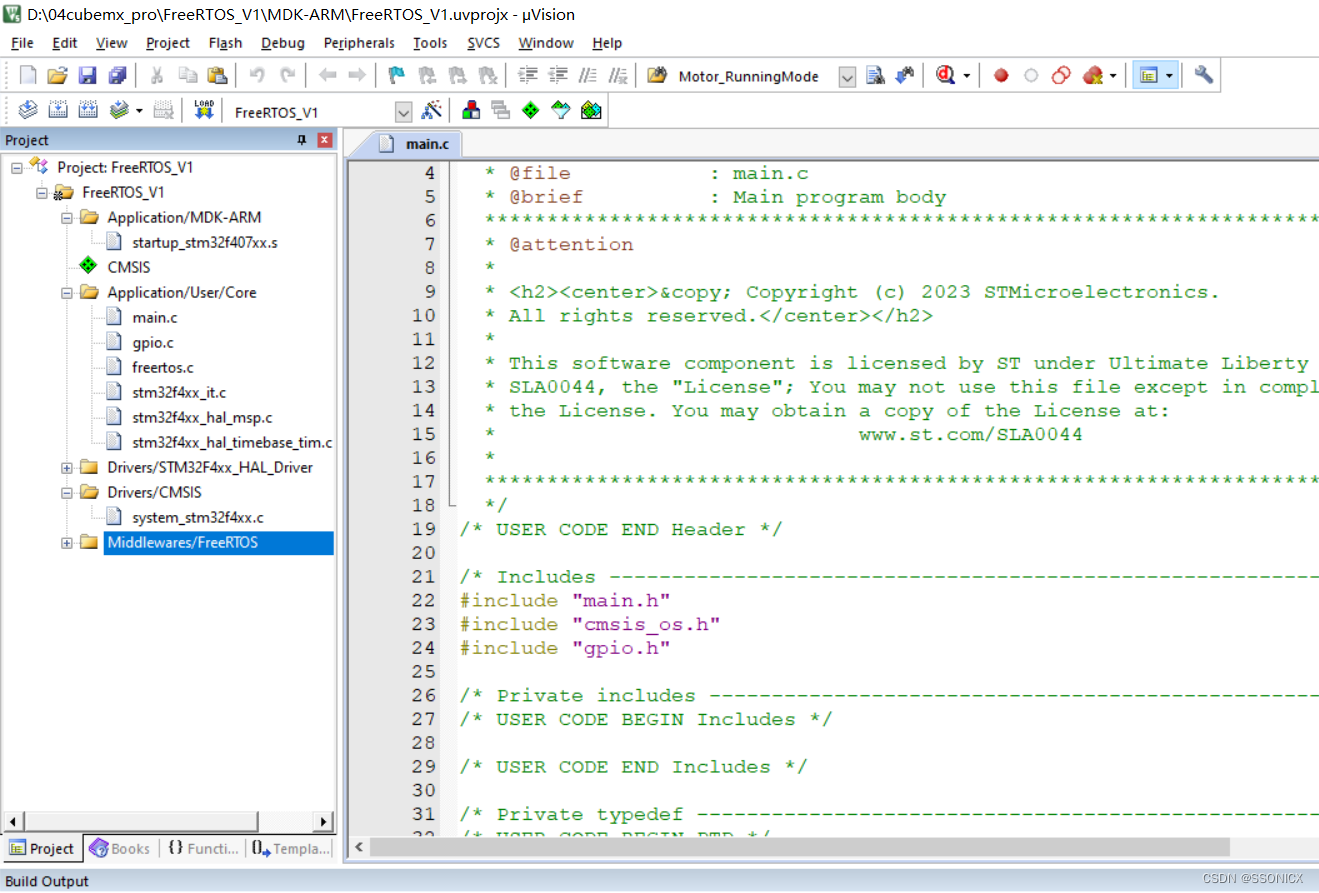

生成的MDKV5的工程目录结构

生成的MDKV5的工程目录结构

相关内容

热门资讯

安卓子系统windows11,...

你知道吗?最近科技圈可是炸开了锅,因为安卓子系统在Windows 11上的兼容性成了大家热议的话题。...

电脑里怎么下载安卓系统,电脑端...

你有没有想过,你的电脑里也能装上安卓系统呢?没错,就是那个让你手机不离手的安卓!今天,就让我来带你一...

索尼相机魔改安卓系统,魔改系统...

你知道吗?最近在摄影圈里掀起了一股热潮,那就是索尼相机魔改安卓系统。这可不是一般的改装,而是让这些专...

安卓系统哪家的最流畅,安卓系统...

你有没有想过,为什么你的手机有时候像蜗牛一样慢吞吞的,而别人的手机却能像风一样快?这背后,其实就是安...

安卓最新系统4.42,深度解析...

你有没有发现,你的安卓手机最近是不是有点儿不一样了?没错,就是那个一直在默默更新的安卓最新系统4.4...

android和安卓什么系统最...

你有没有想过,你的安卓手机到底是用的是什么系统呢?是不是有时候觉得手机卡顿,运行缓慢,其实跟这个系统...

平板装安卓xp系统好,探索复古...

你有没有想过,把安卓系统装到平板上,再配上XP系统,这会是怎样一番景象呢?想象一边享受着安卓的便捷,...

投影仪装安卓系统,开启智能投影...

你有没有想过,家里的老式投影仪也能焕发第二春呢?没错,就是那个曾经陪你熬夜看电影的“老伙计”,现在它...

安卓系统无线车载carplay...

你有没有想过,开车的时候也能享受到苹果设备的便利呢?没错,就是那个让你在日常生活中离不开的iOS系统...

谷歌安卓8系统包,系统包解析与...

你有没有发现,手机更新换代的速度简直就像坐上了火箭呢?这不,最近谷歌又发布了安卓8系统包,听说这个新...

微软平板下软件安卓系统,开启全...

你有没有想过,在微软平板上也能畅享安卓系统的乐趣呢?没错,这就是今天我要跟你分享的神奇故事。想象你手...

coloros是基于安卓系统吗...

你有没有想过,手机里的那个色彩斑斓的界面,背后其实有着一个有趣的故事呢?没错,我要说的就是Color...

安卓神盾系统应用市场,一站式智...

你有没有发现,手机里的安卓神盾系统应用市场最近可是火得一塌糊涂啊!这不,我就来给你好好扒一扒,看看这...

黑莓平板安卓系统升级,解锁无限...

亲爱的读者们,你是否还记得那个曾经风靡一时的黑莓手机?那个标志性的全键盘,那个独特的黑莓体验,如今它...

安卓文件系统采用华为,探索高效...

你知道吗?最近安卓系统在文件管理上可是有了大动作呢!华为这个科技巨头,竟然悄悄地给安卓文件系统来了个...

深度系统能用安卓app,探索智...

你知道吗?现在科技的发展真是让人惊叹不已!今天,我要给你揭秘一个超级酷炫的话题——深度系统能用安卓a...

安卓系统的分区类型,深度解析存...

你有没有发现,你的安卓手机里藏着不少秘密?没错,就是那些神秘的分区类型。今天,就让我带你一探究竟,揭...

安卓系统铠无法兑换,揭秘无法兑...

最近是不是有很多小伙伴在玩安卓系统的游戏,突然发现了一个让人头疼的问题——铠无法兑换!别急,今天就来...

汽车安卓系统崩溃怎么刷,一键刷...

亲爱的车主朋友们,你是否曾遇到过汽车安卓系统崩溃的尴尬时刻?手机系统崩溃还能重启,但汽车系统崩溃了,...

miui系统可以刷安卓p系统吗...

亲爱的手机控们,你是否对MIUI系统情有独钟,同时又对安卓P系统的新鲜功能垂涎欲滴?今天,就让我带你...